|

상세 정보 |

|||

| 시리즈: | i.MX53 | 패키지: | 트레이 |

|---|---|---|---|

| 제품 상태: | 퇴역항공기 | 핵심 프로세서: | ARM® Cortex®-A8 |

| 핵심 / 버스 폭의 수: | 1 핵심, 32-비트 | 속도: | 800MHz |

| 보조처리기 / DSP: | 멀티미디어; 네온™ SIMD | 램 제어기들: | LPDDR2, DDR2, DDR3 |

제품 설명

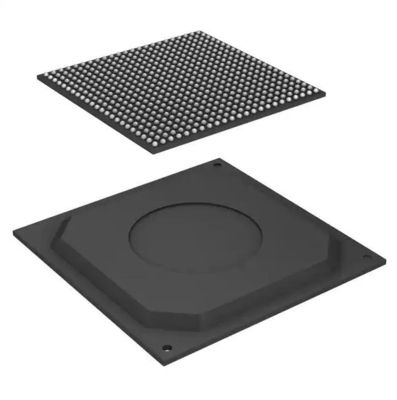

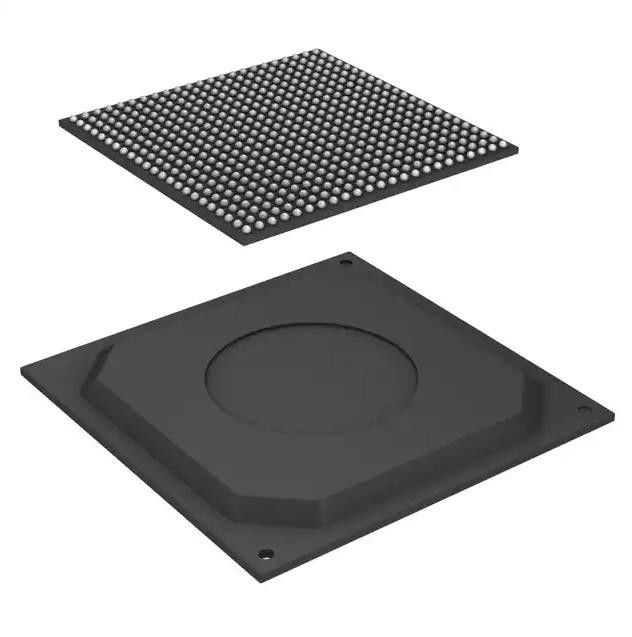

MCIMX537CVV8C 트랜지스터 IC 칩 Ic 마이크로프로세서 유닛 I.Mx53 800 마하즈 529 에프비지에이

ARM® Cortex®-A8 마이크로프로세서 IC i.MX53 1 핵심, 32-비트 800MHz 529-에프비지에이 (19x19)

MCIMX537CVV8C의 상술

| 타입 | 기술 |

| 범주 | 집적 회로 (ICs) |

| 내장됩니다 | |

| 마이크로프로세서 | |

| 엠에프르 | NXP 미국 Inc. |

| 시리즈 | i.MX53 |

| 패키지 | 트레이 |

| 제품 상태 | 퇴역항공기 |

| 핵심 프로세서 | ARM® Cortex®-A8 |

| 핵심 / 버스 폭의 수 | 1 핵심, 32-비트 |

| 속도 | 800MHz |

| 보조처리기 / DSP | 멀티미디어 ; NEONTM SIMD |

| 램 제어기들 | LPDDR2, DDR2, DDR3 |

| 그래픽 가속 | 예 |

| 디스플레이와 인터페이스 제어기들 | 키패드, LCD |

| 이더넷 | 10/100Mbps (1) |

| SATA | SATA 1.5Gbps (1) |

| USB | USB 2.0 (2), USB 2.0 + PHY (2) |

| 전압 - 입출력 | 1.3V, 1.8V, 2.775V, 3.3V |

| 작동 온도 | -40' C ~ 85' C (TA) |

| 보안체 | 무기 TZ, 부트 안전, 암호 기법, RTIC, 안전한 퓨즈 상자, 안전한 JTAG, 보안 메모리, 안전한 RTC, 탬퍼 검출 |

| 증가하는 타입 | 표면 부착 |

| 패키지 / 건 | 529-에프비지에이 |

| 공급자 소자 패키지 | 529-에프비지에이 (19x19) |

| 추가적 인터페이스 | 1-와이어, AC'97이 할 수 있습니다, I2C, I2S, MMC / SD, SAI, SPI, SSI, UART |

| 베이스 상품 다수 | MCIMX537 |

MCIMX537CVV8C의 특징

i.MX53 멀티미디어 응용프로그램 프로세서 (AP통신)은 테폴로윙 특징을 가지고 있는 팔 플랫폼을 기반으로 합니다 :

L1 교육과 L1 데이터 캐시인 오우 MMU

오우 통합된 L2 캐시

핵심 (네온을 포함하여, VFPv3과 L1이 저장합니다)의 오우 최대 주파수 : 800 마하즈

VFPv3을 지원한 오우 네온 보조처리기 (SIMD 매체 처리 아키텍처)과 벡터 플로팅 핵심(VFP-Lite) 보조처리기

오우 트루스트존 기억장치 시스템이 다음과 같은 부품으로 구성되 :

오우 1차 캐시 :

― 교육 (32 키로바이트)

― (32 키로바이트에 관한) 자료를 수집하세요

오우 레벨 2 저장소 :

― 통합된 교육과 자료 (256 키로바이트)

오우 레벨 2 (내부의) 기억 :

― HAB (64 키로바이트)을 포함하여, 부트 롬

― 내부 멀티미디어 / 공유된, 빠른 액세스 RAM (128 키로바이트)

― 안전한 / 비보안 RAM (16 키로바이트)

오우 외부 기억장치 인터페이스 :

― 2 기가바이트에 달하는 16/32 비트 DDR2-800, LV-DDR2-800 또는 DDR3-800

― 32 비트 LPDDR2

― 8/16 비트 NAND SLC / MLC 플래시, 최고 66까지 마하즈, 4/8/14/16 비트 ECC

― 8/16 비트 NOR 플래시, 퍼슈도스태틱 메모리와 셀 방식 RAM.

― 32 비트 멀티플렉스 모드 NOR 플래시, 퍼슈도스태틱 메모리와 셀 방식 RAM.

― 8비트 비동시적 (DTACK 방식) EIM 인터페이스.

― EIM 핀이 인 모두는 다른 인터페이스에 (NFC 핀과 자료)를 먹싱했습니다. 입출력 먹싱 로직은 시스템 기동에 있는 중요한 먹싱으로서, EIM 항구를 선택합니다.

― 목사 4.4에 달하는 에m크를 (혼합 I / 오모드에서) 포함하는 삼성 원난트텀과 운영된 NAND

i.MX53 시스템은 다음과 같은 시스템 온 칩 계면 주위에 구축됩니다 :

오우 64는 (VPU, IPU,GPU3D, GPU2D와 같이) 팔 플랫폼, 멀티미디어 가속기에 의해 사용된 AMBA AXI v1.0 버스와 200 마하즈에 있는 외부 메모리 컨트롤러 (EXTMC) 작동을 물었습니다.

오우 32는 133 마하즈에 작동하는 버스 마스터 주변 기기 중 나머지에 의해 사용된 AMBA AHB 2.0 버스를 물었습니다.

오우 32 비트 IP 버스 주변적 버스는 66 마하즈에 작동하여 대부분의 시스템 주변 기기류의 제어 (과 느린 데이터 교통)을 위해 사용되었습니다.

MCIMX537CVV8C의 애플리케이션

― 최고 1.4까지 MBP를 지원하는 세곳 I2S/SSI/AC97 공항이 각각 오디오에 연결되었습니다

멀티플렉서

4 외부 포트를 제공하는 (AUDMUX).

― 다섯 UART RS232 공항이 각각 4.0 MBP에 상승합니다. 하나는 8개 와이어, 다른 4를 지원합니다

지원

4개 와이어.

― 2 고속도는 CSPI (ECSPI)를 강화했고 프러스 원 CSPI 항구를 포팅시킵니다

― 3 I2

400 킬로보우를 지원한 C 공항

― 고속 이더넷 제어기가 IEEE1588 V1, 10/100으로 순응하기를 계획했습니다

MBP

― 2 콘트롤러 영역은 (FlexCAN) 인터페이스, 1 각각 MBP를 네트워킹합니다

― 소니 필립스 디지털 인터페이스 (SPDIF), Rx와 Tx

― 키 패드 공항 (KPP)

― 2 펄스 폭비 (PWM)

― 인터럽트 능력과 GPIO

환경적이 & MCIMX537CVV8C의 수출 분류

| 특성 | 기술 |

| 로에스 상태 | 순응한 ROHS3 |

| 습도 감지 수준 (MSL) | 3 (168 시간) |

| 한계 상태 | 한계는 영향을 주지 않았습니다 |

| ECCN | 5A992C |

| HTSUS | 8542.31.0001 |

![]()

이 제품에 대한 자세한 내용을 알고 싶습니다